Runner#

This section covers the interface for deciding which workflows to execute, whether to run the in parallel, which specific parameters to use and how to interpret exit/termination codes of tools, as well as gathering/buffering the stdout/stderr and partially processing it. Therefore, the runner API is closely related to Tool, both of them belonging to layer 2 (Workflows) of the Conceptual Model.

In the case of VUnit, the runner is composed by sibling interfaces written in Python and HDL, due to the limitations in some older revisions of VHDL to get the termination status.

TBC

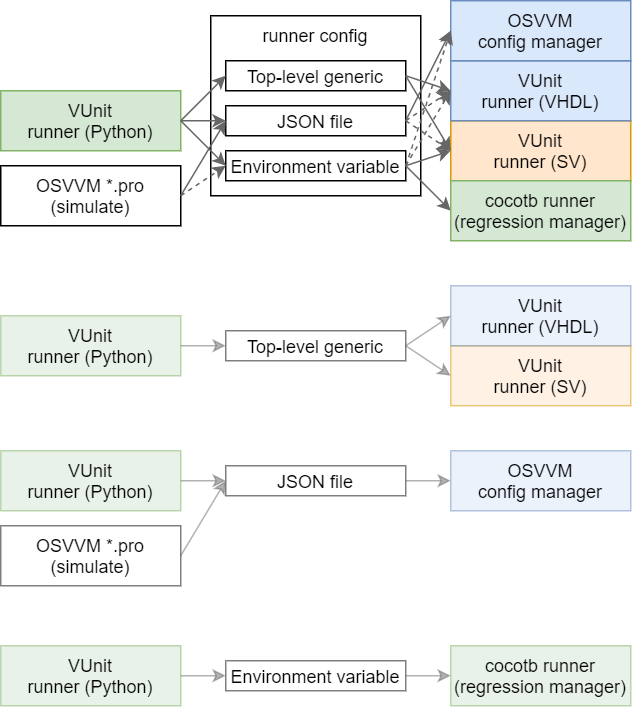

Fig. 4 Strategies to pass the runner configuration from Python to HDL.#

References#

-

gh:python-tap/tappy: a set of tools for working with the TAP in Python.

FuseSoc Verification Automation (fsva) is an HDL testbench runner based on FuseSoc. It fetches targets named with certain patterns in

.corefiles; which can be executed in parallel; stdout/stderr are captured and parsed.