Open Source VHDL Design Explorer (OSVDE)#

OSVDE is GUI for hardware designers to understand and use projects/repositories. It allows exploring the HDL sources, entities/hierarchies, testbenches, tasks, etc. It is mostly meant for VHDL designers (but not only) and particularly for users of VHDL >= 2008.

Important

OSVDE is a proof of concept for prototyping the integration of multiple pieces in the OSVB. It is not actively developed per se, but used as an umbrella for pyVHDLModel, pyGHDL, pyCAPI, etc. A practical usage of the features prototyped in OSVDE is found in Hardware Studio (see umarcor.github.io/hwstudio/doc: Structure).

OSVDE is a GUI tool written in Python only, using tkinter — Python interface to Tcl/Tk, the standard Python interface to the Tk GUI toolkit (see Graphic User Interface FAQ). The motivation for using both Python and tkinter is reducing the dependencies to the bare minimum available on several plataforms. As said, the purpose of OSVDE is not to provide the best performance for (very) large designs, but it’s for prototyping the integration of other pieces such as pyCAPI, pydoit and OSVR.

Installation#

Install a recent version of GHDL and a matching pyGHDL. As explained in Python Interfaces, the following pip command can be used:

pip3 install git+https://github.com/ghdl/ghdl.git@$(ghdl version hash)

Alternatively, get a tarball/zipfile of the GHDL repository, extract it, and set PYTHONPATH accordingly.

Then, retrieve this repository (OSVB) and install the dependencies of pyOSVDE:

pip3 install -r mods/pyOSVDE/requirements.txt

Usage#

Start OSVDE by executing PYTHONPATH=$(pwd)/mods ./mods/pyOSVDE/main.py.

By default, the ‘Open Directory…’ is triggered, asking the user to select a directory containing VHDL sources.

Upon selection, the whole directory is scanned recursively, searching for either *.vhd* or .osvdeignore files,

and all the VHDL sources are added to pyVHDLModel Design as a Document

of a Library.

Then, the Design model is used for generating the content of the GUI.

Hint

Ignore files use the same syntax as regular .gitignore files, and prevent OSVDE from processing some content.

In fact, pypi:gitignore-parser is used for parsing .osvdeignore files.

Attention

Currently, pyGHDL may crash (produce a segmentation fault) if “too many” files are analysed at the same time.

That is actually a bug, because GHDL itself can handle the same sources for simulation and/or synthesis.

While the bug is being fixed, it is recommended to use .osvdeignore files for testing OSVDE with a limited number

of sources.

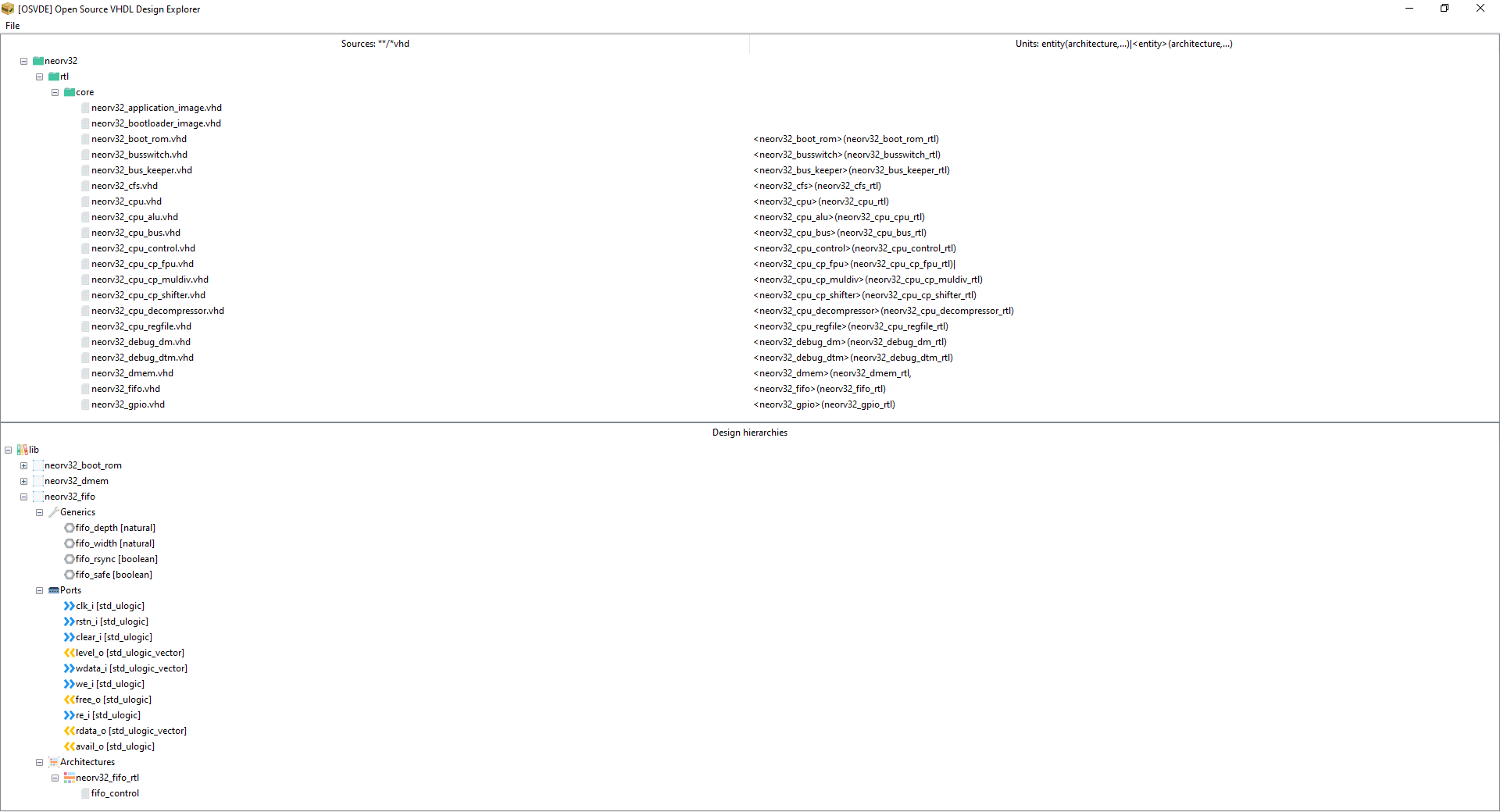

Fig. 3 Repository gh:stnolting/neorv32 opened in OSVDE.#

As shown in Fig. 3, at the top part of OSVDE the hierarchy of the source files is shown. For each VHDL source, a column shows the units (entities and/or architectures) defined in it. As a complement, at the bottom part the logical hierarchy of the units is shown, grouped by library. For each entity, the generics and ports are shown, including the name, type and (for ports only) mode. Architectures are shown too, and within them concurrent statements such as instantiations and generates.

Important

For now, *.vhd* files are scanned only, and all of them are analysed into library lib.

That is because the definition of the Filesets and the Project is out of the scope of OSVDE.

As discussed above, pyCAPI and the project API are to be reused in OSVDE for that purpose.

Future work#

Some enhancements and features we would like to integrate into OSVDE are the following:

Dependency tree and logic hierarchy elaboration through GHDL.

Task running/triggering:

Discovery of VUnit run scripts (see VSCode TerosHDL, VSCode VUnit Test Explorer, Sigasi Studio XPRT).

Discovery of pydoit task definition files (see Tool).

Allow running tasks and showing the results in a window.

‘Edit source in editor’ or ‘Open project in editor’, where IDE is VSCode, (neo)vim, emacs, notepad++…

Pretty printing, formatting…

Customisable style (see gh:jeremiah-c-leary/vhdl-style-guide, gh:VHDLTool).

pyVHDLModel/pyGHDL enhancements:

Preserve comments.

Preserve identifier casing.

OSVDE reference#

- class pyOSVDE.main.OSVDE[source]#

-

- loadDesignTree(parent='')[source]#

Populate the DesignTreeView with the data from the pyVHDLModel Design.

- loadFileTree(parent='')[source]#

Populate the FileTreeView with the data from the pyVHDLModel Design.